– CXL Memory Interconnect Initiative: Enabling a New Era of Data Center Architecture – How PCIe 5 Can Accelerate AI and ML Applications Specifically, the data center is shifting from a model where each server has dedicated processing and memory-as well as networking devices and accelerators-to a disaggregated “pooling” paradigm that intelligently matches resources and workloads. Server architecture-which has remained largely unaltered for decades-is now taking a revolutionary step forward to address the yottabytes of data generated by AI/ML applications. Industry Landscape: Why is a new class of Interconnect needed?Įxponential data growth is prompting the semiconductor industry to embark on a groundbreaking architectural shift to fundamentally change the performance, efficiency, and cost of data centers. Compute Express Link vs PCIe 5: How Are These Two Related?ġ.An Introduction to CXL: What Is Compute Express Link?.Industry Landscape: Why Is a New Class of Interconnect Needed?.These solutions are now available with integrated Integrity and Data Encryption (IDE) modules which monitor and protect against cyber and physical attacks on CXL and PCIe links. Lastly, we review Rambus CXL solutions, which include the Rambus CXL 2.0 Interconnect Subsystem comprising a CXL 2.0 Controller and CXL 2.0 SerDes PHY.

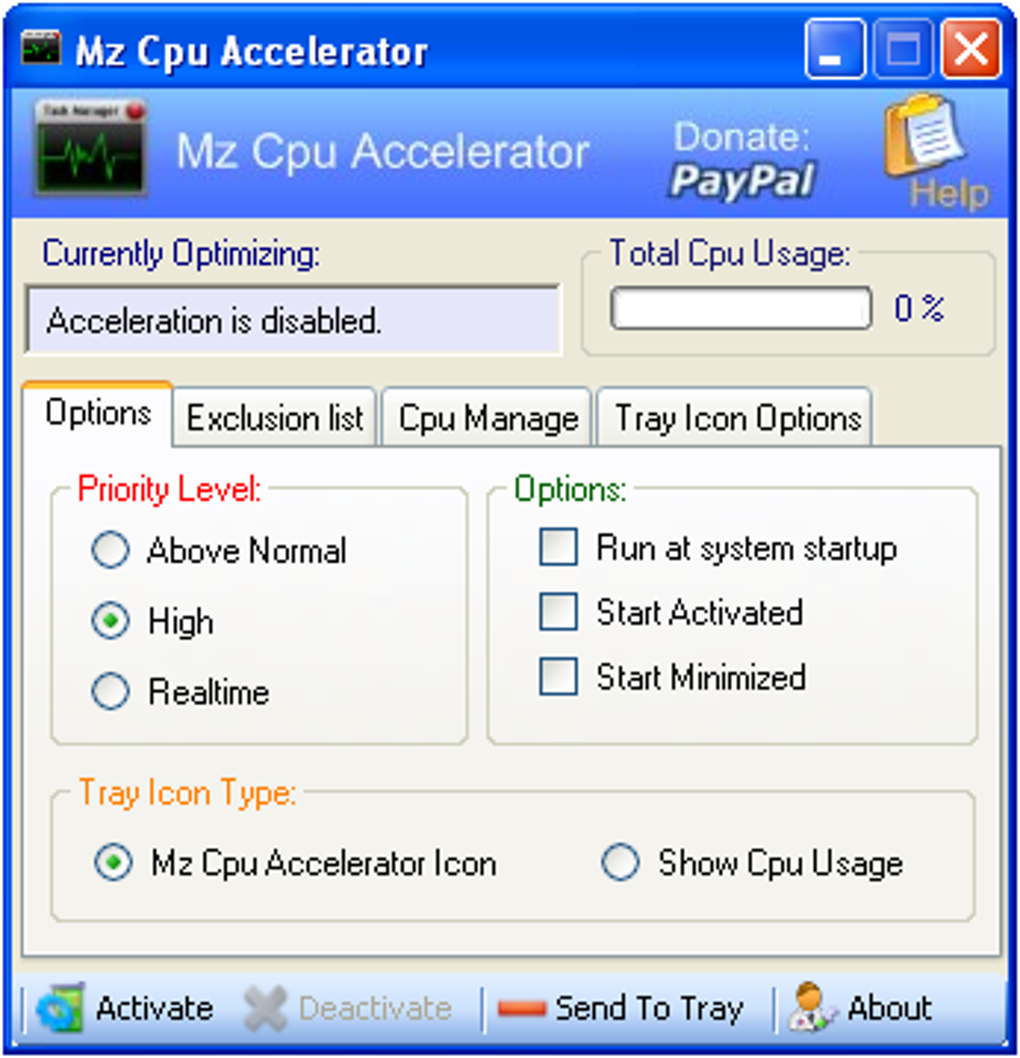

#CPU SPEED ACCELERATOR 6.0 SOFTWARE#

#CPU SPEED ACCELERATOR 6.0 DRIVER#

Non-Volatile DDR4 Registering Clock Driver.Video Compression and Forward Error Correction Cores.At Rambus, we create cutting-edge semiconductor and IP products, spanning memory and interfaces to security, smart sensors and lighting.

0 kommentar(er)

0 kommentar(er)